| 【精选】对PCIE设备访问及其配置空间的一点理解 | 您所在的位置:网站首页 › pcie 配置空间 › 【精选】对PCIE设备访问及其配置空间的一点理解 |

【精选】对PCIE设备访问及其配置空间的一点理解

|

讲讲对PCIE总线协议的一点理解吧。感觉每一年又会多一点理解,但不懂得地方仍很多。 PCI总线是拓扑结构,PCI总线从0开始,不超过256(但一般不会一层一层挂太多)。Device不超过32,Function不超过8。如下图,挂在总线0,即Bus 0上的为根(root)设备,下面还挂设备的则为桥(Bridge),不再挂设备的即为设备(Device)。挂在桥下的设备总线号必然大于桥的总线号,下图中,PCI桥片1位Bus 0,PCI设备11为bus 1,PCI设备31为Bus 3。所以PCI桥片1的从属总线是1-3。 首先要判断Class Code的高位为0x0c(串行总线控制器),才能找到0x0c对应的Sub-Class Code,代码对应下图: 如何访问PCI设备? 两种方式:IO或memory IO:即地址端口0xcf8/数据端口0xcfc,特定Bus,Device,Function按下图方式得到地址(实际中寄存器地址不用偏移两位),写入0xcf8;从0xcfc得到数据。 |

【本文地址】

公司简介

联系我们

挂在PCI总线上的所有桥或设备都有特定的编号,即为Bus,Device,Function,不会重复。CPU对于挂在root上的设备都有固定定义,查看datasheet即可。

挂在PCI总线上的所有桥或设备都有特定的编号,即为Bus,Device,Function,不会重复。CPU对于挂在root上的设备都有固定定义,查看datasheet即可。  PCI设备的配置空间如下图:

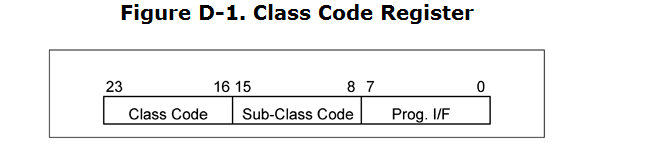

PCI设备的配置空间如下图:  该空间寄存器的详细信息可查看PCIE Spec,以Class Code为例,Class Code是判断PCI类型:LAN、VGA、存储设备等等。对于下面一段代码进行分析。

该空间寄存器的详细信息可查看PCIE Spec,以Class Code为例,Class Code是判断PCI类型:LAN、VGA、存储设备等等。对于下面一段代码进行分析。

memory:方式类似,但Bus,Device,Function全部左移四位,bit31-28也根据CPU不同而不同,以Intel为例:Address = 0xE0000000+(Bus

memory:方式类似,但Bus,Device,Function全部左移四位,bit31-28也根据CPU不同而不同,以Intel为例:Address = 0xE0000000+(Bus